Information in this document is subject to change without notice and does not represent a commitment on the part of microsoft Corporation. The software described in this document is furnished under a license agreement. It is against the law to copy the MSX lechnical Reference Documentation in magnetic tape, disk or any other medium for any purpose other than for evaluation purposes.

(C) Microsoft Corporation 1983

Comments about this documentation may be sent to:

Microsoft Corporation Microsoft Building 10700 Northup Way Bellevue, WA 98004

Microsoft is a registered trademark of Microsoft Corporation. MS is a registered trademark of Microsoft Corporation. MSX is a registered trademark of Microsoft Corporation.

# MSC TECHNICAL REFERENCE DOCUMENT INDEX

- I. HARDWARE SPECIFICATION

- II. MSX-DOS SYSTEM CALL SPECIFICATION

- III. MSX-BASIC LANGUAGE SPECIFICATION

- IV. BIOS ENTRY POINT LIST

- V. BIOS WORK AREA LIST

- VI. SLOT MANAGEMENT MECHANISM

### MSX HOME PERSONAL COMPUTER SYSTEM

HARDWARE SPECIFICATION

(RELEASE 3.1)

04/05/84

(C) 1983 by Microsoft Corporation

All information contained nerein is proprietary to Microsoft

### CONTENTS

- 1. SUMMARY OF HARDWARE

- 1.1 SPECIFICATION

- 1.2 SYSTEM CONFIGURATION

- 2. HARDWARE SPECIFICATION

- 2.1 151

- 2.2 MEMORY

- 2.3 INTERRUPT

- 2.4 SCREEN DISPLAY

- 2.5 KEYBOARD

- 2.6 SOUND

- 2.7 CASSETTE INTERFACE

- 2.8 INPUT/OUTPUT PORT

- 2.9 PRINTER INTERFACE

- 2.10 FLOPPY DISK INTERFACE

- 3. CARTRIDGE

- 3.1 SPECIFICATION OF CARTRIDGE

- 3.2 CARTRIDGE BUS

- 3.3 CONDITION OF CARTRIDGE BUS CONNECTION

- 3.4 POWER CAPACITY

- 4. ADDRESS MAP

- 4.1 MEMORY MAP

- 4.2 I/O ADDRESS MAP

- 4.3 I/O DEVICE DESCRIPTION

- 4.3.1 RS-232C

- 4.3.1.1 LSI COMPONENTS -

- 4.3.1.2 PORT ADDRESSES -

- 4.3.1.3 THE USAGE OF SWITCH PORT AT ADDRESS 82H AND 83H -

- 4.3.1.4 THE USAGE OF 8253 TIMER-COUNTER TO GENERATYE BAUD RATE CLOCK 4.3.2 PRINTER PORT

- 4.3.2.1 PORT ADDRESS -

- 4.3.3 VDP PORT

- 4.3.4 PSG PORT

- 4.3.5 PPI PORT

- 4.3.6 EXTERNAL MEMORY (SONY)

- 4.3.7 LIGHT PEN (SANYO)

- 4.3.5 ALDIO/VIDEO CONTOL

- 4.4 NOTE UN 1/0 ADDRESS ASSIGNMENTS

- 4.4 PPI BIT ASSIGNMENT

- 4.5 PSG BIT ASSIGNMENT

- 4.6 PSG BIT ASSIGNMENT

#### APPENDIX

- A. LIST OF CONNECTORS

- B. NOTES FOR SYSTEM EXPANSION

- C. SLOTS

- D. EXAMPLE OF I/O PORT CONNECTION

Hardware specification for MSX HOME PERSONAL COMPUTER SYSTEM

\*This document specifies the U.S./European version of MSX system.

# CHAPTER 1 SUMMARY OF HARDWARE

#### SUMMARY OF HARDWARE

### 1.1 SPECIFICATION

1.1.1 Required Components

CPL 4 MHz Z-8UA compatible

n Memory RCM 32K (MSX system software)

RAP minimum &k (16K\* resommended)

o Screen Display Text display capability  $40 \times 24$  (refer to section 2.4)

Graphic 256 x 192 Color 16

color 16

o Cassette tape FSK format 1200/2400 Baud

Sound 8 Octave, 3 Voices

o Character Set Alphanumeric, Japanese, Graphic (Japanese version)

Alphanumeric, European, Graphic (International version)

o Keyboard U.S./Europe, French\*, German\*, Japanese

o Expansion Slot Software cartridge, expansion BUS slots

o Joystick 1 or 2\*

1.1.2 Recommended Extensions for U.S./Europe

o Memory RAM 64K\* total

o Expansion Slot Second

Video RF output

1.1.3 Standardized Optional Extensions

o Screen Display\* 80-column text

o Clock\* Battery backed-up CMOS

o Communications\* RS-232

o Floppy Disk\* According to each company. Format is MS-DOS compatible

o Printer\* 8 bit parallel

\* Items with asterisk may not be build—in in the minimum system.

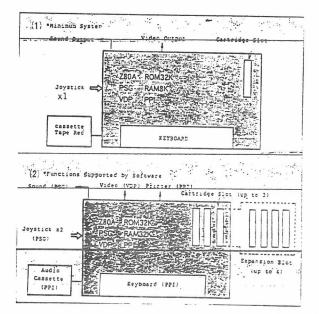

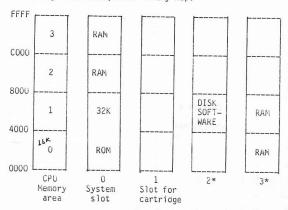

### 1.2 SYSTEM CONFIGURATION

C-APTER 2

HARDWARE SPECIFICATION

### 2.1 LSI

o CPII

Z-80A Compatible CLOCK 3.579545MHz (NTSC Color sub carrier frequency)

1 WAIT in M1 CYCLE

VDP

TI TMS-9918A Compatible

o PSG

GI AY-3-8910 Compatible

o PPI

Intel i-8255 Compatible

# 2.2 MEMORY

o ROM

MSX BASIC 32KB

o RAM

8KB or more

### NOTE

Basic unit has four logical slots, so the total memory space can be expanded up to 256KB. Each logical slot can be expanded to have up to 4 physical slots, total of 16 slots. So in this case, maximum memory scace is 1 megabyte.

BASIC ROM occupies address 0 to 7FFF, RAM address starts from FFFF and grows downward on the memory map to 8000.

For details refer to 4.1 memory map.

For U.S. Market we recommend 64K so the machine can easily be upgradable to MSX-DOS, although BASIC ROM will only use 32K RAM.

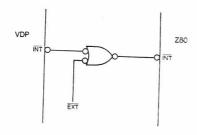

### 2.3 INTERRUPT

MNI Not used. MSX ROM only provides PAM hook.

O INT Accept interrupts from VDP and cartridge. The interrupt is Z-80 mode 1. (Branch to 38H) MSX system software uses interrupt from VDP for timer count. The interval of the interrupt is 60Hz in NTSC and 50Hz in PAL/SECAM version.

#### NOTE

It is not possible to support NMI under MSX DOS environment because address 66H, which is the entry vector for NMI, is occupied by FCB data for DOS.

#### 2.4 SCREEN DISPLAY

o LSI

TI TMS9918A Compatible

o Character set

Alphanumerical + European + Graphic 256 patterns 6x8 dots

o Color

16 colors

o Sprites

32 sprites. Maximum 4 sprites on the same horizontal line.

o List of display modes

| M ()    | DE                 | RES.      | SIZE            | νο. | COLOR                  | SPRITE | NUMBER<br>OF<br>CHARACTERS |

|---------|--------------------|-----------|-----------------|-----|------------------------|--------|----------------------------|

| Graphic | LSI<br>Spec.       | 256 x 192 | 8 x 8           | 056 | 16                     | WE S   | 32 x 24                    |

| I       | Suggested<br>value | 240 x 192 | 8 X 8           | 256 | 16<br>colors           | YES    | 29 x 24                    |

| Graphic | LSI<br>Spec.       | 256 x 192 | 0               | 760 |                        | VLS    | 32 x 24                    |

| 11      | Suggested<br>value | 240 x 192 | 8 x 5           | 768 | 16<br>colors           | YES -  | 29 x 24                    |

| Multi-  | LSI<br>Spec.       | 64x48b1k  |                 |     |                        | NO .   | 32 x 24                    |

| color   | Suggested<br>value | 64x4Ublk  | 4 x 4<br>/block | -   | colors                 |        | 29 x 24                    |

| Text    | LSI<br>Spec.       | 256 x 192 |                 | 0.5 | 2<br>colors            |        | 40 x 24                    |

| IEXC    | Suggestea<br>value | 240 x 192 | бхо             | 256 | out of<br>16<br>colors | YES    | 39 x 24                    |

Suggested value to use: the 8 pixels from left and right of rorizontal are not used by software.

Δ The number of patterns

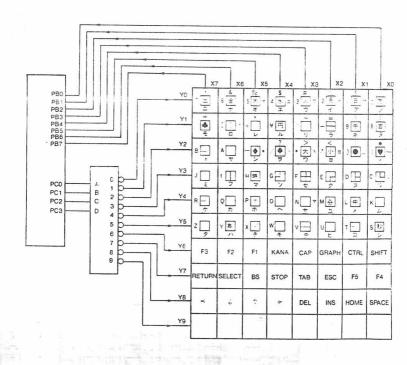

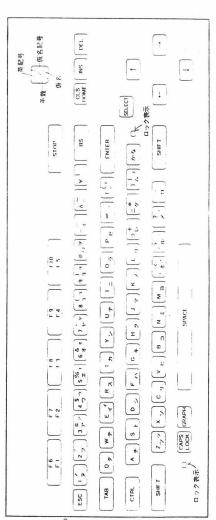

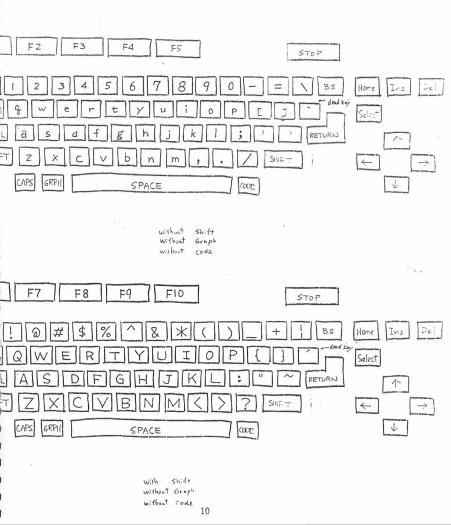

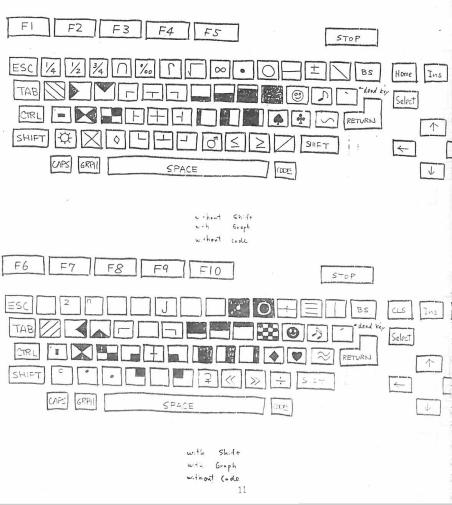

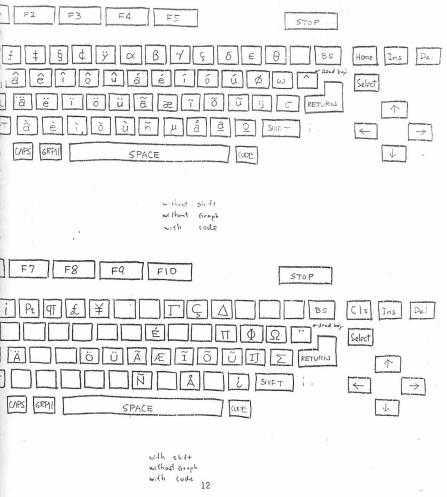

### 2.5 KEYBOARD

o Layout

Refer to figure U.S./European French German

o Scanning

Software scanning driven by VDP interrupt

- o Number of keys 70 plus optional dead key

- o Matrix diagram

|   | v.       |                   |                                                   | _                                        |                                        |                        |                                  |                            |                                  |               |                                   |                                         |                                             | ν.     |                                  |            | (4)                                                                                          |   |

|---|----------|-------------------|---------------------------------------------------|------------------------------------------|----------------------------------------|------------------------|----------------------------------|----------------------------|----------------------------------|---------------|-----------------------------------|-----------------------------------------|---------------------------------------------|--------|----------------------------------|------------|----------------------------------------------------------------------------------------------|---|

| - | /        | X                 | 0                                                 | 1./                                      |                                        | 4                      | 2                                | 3                          | 3                                | 4             | ٤.                                | 5                                       | <del>:</del>                                | E      | 6                                | . 1        | 7                                                                                            |   |

|   | Υ        | PRI DOO           | char  cod                                         | char                                     | code                                   | char                   | code                             | char                       | code                             | char          | code                              | char                                    | code                                        | char   | code                             | cnar       | code                                                                                         |   |

|   | 0        | S.<br>G           | 0 30<br>0 25<br>0 0<br>6 0<br>6 E                 | !<br>9 1/4_<br>N F                       | 9F                                     | 2 0 1/2 + Pt           |                                  | 3#34 00                    | 33<br>23<br>BA<br>FC<br>BE       | 4\$0 44       | 34<br>24<br>EF<br>98              | 5%% :Y ¥                                | 35<br>25<br>BD<br>98<br>9D                  | 6.     | 36<br>5E<br>F4<br>FS<br>E0       | 7 & F      | 37<br>26<br>FB<br>E:                                                                         |   |

|   | <i>†</i> | G S<br>C .        | 8 31<br><b>★</b> 2/<br><b>※</b> E/<br><b>↑</b> E/ | 9. ( · · · · · · · · · · · · · · · · · · | 3.9<br>2.8<br>0.7<br>0.8<br>8.7<br>8.0 | -<br>-<br>+<br>E       | 2D<br>5F<br>17<br>1F<br>EE       | +,+       o ·              | 3 D<br>2 B<br>F 1<br>F 0<br>E 9  | 2/-/          | 5 C<br>7 C<br>1 E<br>1 6          | 0 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | 5B 7B 01 0 0 D E E E                        | Ţ.     | 5D<br>7D<br>0D<br>0E<br>DA<br>EA | 7. F.( • • | 3B<br>3A<br>06<br>04<br>07<br>06                                                             |   |

|   | 2        | G S C S C S       | / 2                                               | ≈<br>  ~                                 | 60<br>7E<br>8B<br>F7<br>E5<br>E4       | , < <u>&lt; </u> (a. A | 2C<br>3C<br>F3<br>AE<br>86<br>8F | >.<br>>.<br>>.<br>>.<br>a. | 3 E<br>F 2<br>A F<br>A 6         | V: 101-1-     | 2F<br>3F<br>1D<br>F6<br>A7<br>A8  | 0 12 13 14 1/ 1 1                       | —dead key —                                 | a A    | 61<br>41<br>C4<br>FE<br>84<br>8E | ù          | .62<br>.42<br>.11                                                                            |   |

|   | 3        | G<br>G S<br>. C S | c 6:<br>C 4:<br>♦ B0                              | 0 D                                      | 64<br>44<br>C7<br>C1<br>88             | e E ← .                | 65<br>45<br>CD<br>CE<br>8C       | 0:0:                       | 66<br>46<br>14<br>04<br>94<br>99 | C: r: + - 0 m | 67<br>47<br>15<br>10<br>81<br>9 A | E I H I I                               | 6 0 1 5 D D D D D D D D D D D D D D D D D D |        | 69<br>49                         |            | 6 4 5 6 6 9 9                                                                                |   |

|   | 4        | G S C S           | K 66 K 41 D.C                                     |                                          | 60<br>40<br>08<br>09<br>84             | 10 Q X 3               | 4 D                              | ç .z                       | 6E<br>4E<br>1B<br>03<br>A4<br>A5 | 0. 0          | 6F<br>4F<br>C2<br>C3<br>A2        | O. D.                                   | 70<br>50<br>05<br>07<br>43<br>E3            | (d)    | 71<br>51<br>CB<br>83             | c & 기기 & 그 | 5 0<br>1 0<br>1 0<br>2 0<br>3 |   |

|   | 5        | G S               | s 7:<br>S 5:<br>D:<br>D:<br>ë 8:                  |                                          | 74<br>54<br>12<br>96                   | UUVENE                 | 75<br>55<br>CO<br>C5<br>82       |                            | 76<br>56<br>1A<br>05<br>95       | w.<br>W       | 77<br>57<br>CF<br>DO<br>88        | ×                                       | 7 6 6 6 6 A                                 | y<br>Y | 7 9 9 1 A A O                    | Z          | 5 A O F 8 5                                                                                  | • |

c Keyboard layout

The following keyboard diagrams contain an optional dead-key. This dead-key is useful for European accented character input. For example, when one wishes to enter "â", one must first press the dead-key "^" and then press "a".

The dead-key will not be useful in the U.S. or U.K. Nor will it be useful in France and Germany, where specific French and German keyboards have been designed which include different dead-keys. Therefore this general dead-key should only be included on machines which will be marketed into minor European countries.

The keyboard diagrams show the dead-key to the left of the carraige return key, but this is probably not a good place for it, because it pushes the carraige return key too far to the right. Manufacturers may place this key where they wish.

MSX French Keyboard Caps Lock shifts numeric keys and )/<sup>0</sup> key. Dead keys are shaded. Manufacturer may move less than departer than key to lower left but must do so in keyboard hardware

|                                                                                                     | OTHER DESIGNATION.         |                    |               |                       |            |

|-----------------------------------------------------------------------------------------------------|----------------------------|--------------------|---------------|-----------------------|------------|

| are.                                                                                                | ¥                          | -                  | ı             |                       |            |

| MINITAM                                                                                             | ^ V                        |                    | ω <b>*</b> !s | Q.                    | N.         |

| manuracturer may move less changgreater than key to lower leit but must do so in keyboard nardware. | lι                         | \$                 |               | $\vdash$              | -          |

| N III K                                                                                             | • -                        | g c                | 2,3           | + 11                  | CODE       |

| on                                                                                                  |                            | ۵۰                 | Σ             | <b>\</b>              | 5          |

| nius c                                                                                              | 0 .4                       | . i                |               |                       |            |

| ר חחר                                                                                               | <b>6</b> 5                 |                    | Ä             |                       |            |

| בו                                                                                                  | 8 -                        | -                  |               | 3                     |            |

| MO                                                                                                  |                            |                    |               | l<br>Iz               | 1 I        |

| ey to                                                                                               | r .0                       |                    | Ξ             |                       |            |

| ndn k                                                                                               |                            | ^                  | 5             | 8                     |            |

| בו                                                                                                  | 9 5                        | _                  |               | >                     |            |

| dreat                                                                                               | 25 -                       |                    |               |                       |            |

| LIIdii                                                                                              | 4 .                        | æ                  | ۵             | 0                     |            |

| 22                                                                                                  |                            | us.                |               | ×                     | H          |

| a none                                                                                              | e :                        |                    | S             | 8                     | GRAPH      |

| ılldy                                                                                               | 6.2                        | 200 m              | a             |                       | <b>(2)</b> |

| ic tur e.                                                                                           |                            | 1                  |               |                       |            |

| nure                                                                                                | - 00                       | TAB                | E.            | $\Diamond$            |            |

| IJ G                                                                                                | Esc                        |                    |               |                       |            |

|                                                                                                     | Calculation of the Control | and its section is |               | and the second second | _          |

Caps Lock shifts A, O, and U umlaut keys. Dead keys are shaded. Manufacturer may move less than/greater than key to lower left but must do so in keyboard hardware. MSX German Keyboard

|                                         | +                     | -      | 1          |   |            |

|-----------------------------------------|-----------------------|--------|------------|---|------------|

|                                         | \<br>\<br>\<br>\<br>\ | • +    | < %        | Û |            |

|                                         | -1.                   | :D     | : <b>4</b> |   |            |

|                                         | ~ 5                   | ۵      | :0         |   | CODE       |

|                                         | ۰ ٥                   | . 0    | 7          |   |            |

|                                         | - 6                   |        | ×          | W |            |

| 100000000000000000000000000000000000000 | ~ 80                  |        | -          |   |            |

|                                         | 1 /                   | n z    | Ξ          | 8 |            |

|                                         | 8 9                   | _      | 9          | ^ |            |

|                                         | % ro                  | Я      | L.         | S |            |

|                                         | S 4                   | m<br>D | ٥          | × | F          |

|                                         | 9 6                   | 8      | s .        | > | GRAPH      |

|                                         | : 2                   |        | < -        |   | <b>(P)</b> |

|                                         | Esc 1                 | TAB    | Ctrl       | 0 |            |

### BASIC SPECIFICATION

### 2.6 SOUND

o LSI

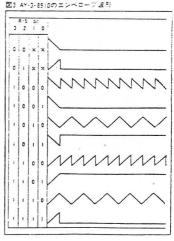

GI AY-3-8910 Compatible

o OCTAVE

8 Octaves (3 Voices output)

o SOUND EFFECT Yes

SOFTWARE SOUND OUTPUT 1 bit from output port

o OUTPUT LEVEL -5dbm (If the system has output connector)

o CONNECTOR RCA 2 pins (If the system has audio output connector)

| 8-BT Fine<br>8-BT Fine<br>8-BT Fine<br>losse | 4-8<br>e Tune B<br>4-B<br>e Tune C<br>4-8 | #T Coar                                                           | rse Tune rse Tune rse Tune rse Tune Tone B                                   | В                                           |  |  |  |

|----------------------------------------------|-------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|--|--|--|

| 8-BIT Fine                                   | 4-B<br>4-B<br>e Tune C<br>4-B<br>5-B/T F  | ST Coar                                                           | rse Tune<br>rse Tune<br>Control                                              | B<br>C                                      |  |  |  |

| 8-BIT Fine                                   | 4-B<br>e Tune C<br>4-B<br>5-B/T F         | FT Coar                                                           | rse Tune<br>Control                                                          | c                                           |  |  |  |

| lorse<br>B                                   | e Tune C<br>4-8<br>5-BIT F                | Penod C                                                           | rse Tune<br>Control                                                          | c                                           |  |  |  |

| lorse<br>B                                   | 4-8<br>5-B/T F                            | Period C                                                          | Tone                                                                         |                                             |  |  |  |

| ; B                                          | 5-BIT F                                   | Penod (                                                           | Tone                                                                         |                                             |  |  |  |

| ; B                                          |                                           |                                                                   | Tone                                                                         | A                                           |  |  |  |

| ; B                                          | Α.                                        | С                                                                 |                                                                              | 4                                           |  |  |  |

|                                              | Α.                                        | С                                                                 | 2                                                                            | A                                           |  |  |  |

|                                              |                                           |                                                                   | -                                                                            |                                             |  |  |  |

| M                                            | L3 .                                      | 2                                                                 |                                                                              | L2                                          |  |  |  |

| . M                                          | L3                                        | L2                                                                | · ·                                                                          |                                             |  |  |  |

| : 4                                          | 73                                        | 12                                                                | U                                                                            | LS.                                         |  |  |  |

| 8-BIT FINE                                   | e Tune E                                  |                                                                   |                                                                              |                                             |  |  |  |

| .8-BIT Coarse Tune E                         |                                           |                                                                   |                                                                              |                                             |  |  |  |

|                                              | CONT                                      | ATT.                                                              | AL-                                                                          | HOLD                                        |  |  |  |

| PARALLE.                                     | no C 1 _                                  | Port A                                                            |                                                                              |                                             |  |  |  |

| T PAPALLE                                    | EL : C a                                  | n 22r:                                                            | â                                                                            |                                             |  |  |  |

|                                              | 8-BIT Coar                                | 8-BIT Fine Tune E<br>8-BIT Coarse Tune<br>CONT<br>PARALLEL I O on | 8-BIT Fine Tune E<br>BIT Coarse Tune E<br>CONT ATT<br>PARALLEL I O on Port A | 8-BIT Fine Tune E<br>-BIT Coarse Tune E<br> |  |  |  |

#### 2.7 CASSETTE INTERFACE

INPUT From the earphone terminal of tape recorder

OUTPUT To the microphone terminal of tape recorder

SYNCHRONIZATION Asynchronous by the software

O BAUD RATE 1200 Baud (1200Hz - 1 wave "0", 2400Hz - 2 waves "1") (Default)

2400 Baud (2400Hz - 1 wave "0", 4800Hz - 2 waves "1")

Change by software

(Tape recorder may have to be specified by the

manufacturer when used under 2400 Baud mode)

FSK (Frequency Shift Keying) by the software o MUDULATION

DEMODULATION By the software. The system software automatically

detects the baud rate when receiving the data.

o MOTOR CONTROL

Yes

DIN 45326 (8 pin) o CONNECTOR

O TABLE OF SIGNAL PINS

| PIN NO. | SIGNAL<br>NAME | DIRECTION | PIN CONNECTION |

|---------|----------------|-----------|----------------|

| 1       | GND            |           |                |

| 2       | GND            |           |                |

| 3       | GND            |           | 7 6            |

| 4       | CMTOUT         | OUTPUT    | (S) (D)        |

| 5       | CMTIN          | INPUT     | (S) (E)        |

| 6       | REMOTE +       | OUTPUT    | 2              |

| 7       | REMOTE -       | OUTPUT    |                |

| 8       | GNO            |           |                |

2.8 INPUT/OUTPUT (JOYSTICK) PORT (1 OR 2\* PORTS)

o LSI

AY-3-8910 compatible

o I/0

Input 4 bit, output 1 bit, digirectional 2 bit per each

port

o LOGIC

Active high

o LEVEL

TTL

o CONNECTOR

AMP 9 pin compatible

O LIST OF PINS

| IN NO. | SIGNAL<br>NAME    | DIRECTION        | PIN CONNECTION |

|--------|-------------------|------------------|----------------|

| 1      | FWD               | INPUT            |                |

| 2      | BACK              | INPUT            |                |

| 3      | LEFT              | INPUT            |                |

| 4      | RIGHT             | INPUT            |                |

| 5      | + 5V <sup>Δ</sup> |                  | 00000          |

| 6      | TRG 1             | INPUT/<br>OUTPUT | <b>6089</b>    |

| 7      | TRG 2             | OUTPUT           |                |

| 8      | OUTPUT            | OUTPUT           |                |

| 9      | GND               |                  |                |

$\Delta$  Current capacity is 50mA each

### 2.9 \*PRINTER INTERFACE

o SPECIFICATION 8 bit parallel Handshakes by BUSY and STROBE signal

o LEVEL TTL

O CHARACTER CODE SAME AS MSX DISPLAY CODE

o CONNECTOR AMP 14 pin compatible

o LIST OF PINS

| PIN NO. | SIGNAL<br>NAME | PI  | N CO | NNEC | IOIT | V  |    |   |    |   |

|---------|----------------|-----|------|------|------|----|----|---|----|---|

| 1       | PSTB           |     |      |      |      |    |    |   |    |   |

| 2       | PDBO           |     |      |      |      |    |    |   |    |   |

| 3       | PD61           |     |      |      |      |    |    |   |    |   |

| 4       | PDB2           |     |      |      |      |    |    |   |    |   |

| 5       | PDB3           |     |      |      |      |    |    |   | -  |   |

| 6       | PDB4           |     |      |      | Γ.   | Γ. |    |   | Γ. |   |

| 7       | PDB5           | \ _ | 7    | 6    | 5    | 4  | 3  | 2 | 1  | _ |

| 8       | PDB6           | L   |      | Г    |      |    |    |   |    |   |

| 9       | PD67           |     | 14   | 13   | 12   | 11 | 10 | 9 | 8  |   |

| 10      | N.C.           |     |      |      |      |    |    |   |    |   |

| 11      | BUSY           |     |      |      |      |    |    |   |    |   |

| 12      | N.C.           |     |      |      |      |    |    |   |    |   |

| 13      | N.C.           |     |      |      |      |    |    |   |    |   |

| 14      | GND            |     |      |      |      |    |    |   |    |   |

### 2.10 FLOPPY DISK INTERFACE

- o Contains 16K bytes of ROM at 4000H that includes:

- \* MSX-DUS KEP VEL

- \* MSX DISK BASIC

- \* PHYSICAL DISK I/O DRIVER (Supplied by each manufacturer)

- The hardware interface is not specified. The physical disk I/O driver supplied by manufacturer should virtualize hardware differences.

- O It is desirable to have a mechanism in the disk drive to detect whether the crive door has been opened. It reduces disk accesses which check for disk changes.

- o Floppy formats are MS-DOS compatible

| 8 inch     | SD  | 128 byte/sector                               |

|------------|-----|-----------------------------------------------|

| 8 inch     | DD  | 1024 byte/sector                              |

| 5-1/4 incn | DD  | 512 byte/sector                               |

| 3.5 inch   | CFD | 512 byte/sector (exactly same as 5-1/4" 96TPI |

| 3 inch     | CFD | 512 byte/sector (exactly same as 5-1/4" 46TPI |

CHAPTER 3

CARTRIDGE

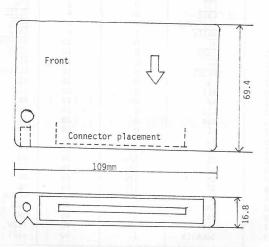

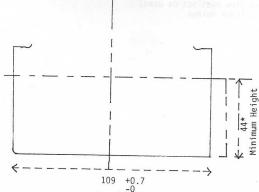

The internal specification of standard size cartridge (all measurements in mm)

Specification of extended size cartridge.

<sup>\*</sup> No standard will be enforced beyond the above minimum height

### CARTRIDGE

### 3.2 CARTRIDGE BUS

### o LIST OF SIGNAL PINS

| PIN NO.               | NAME       | I/0 *       | PIN NO. | NAME     | I/0 *                                                                                            |

|-----------------------|------------|-------------|---------|----------|--------------------------------------------------------------------------------------------------|

| 1                     | <u>rs1</u> | 0           | 2       | CS2      | 0                                                                                                |

| 3                     | CS12       | 0           | 2 4     | SLTSL    | 0<br>0<br>0<br>1<br>1<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

| 1<br>3<br>5<br>7<br>9 | RESERVED   | _           | 6       | RFSH     | 0                                                                                                |

| 7                     | WAITA      | I           | 8       | INTA     | Ī                                                                                                |

| á                     | MI         | Ô           | 10      | BUSDIR   | I                                                                                                |

| 11                    | IORQ       | 0           | 12      | MERQ     | Ō                                                                                                |

| 13                    | WR         | Ö           | 14      | RD       | 0                                                                                                |

| 15                    | RESET      | Ö           | 16      | RESERVED | 72                                                                                               |

| 17                    | A9         | o o         | 18      | A15      | 0                                                                                                |

| 19                    | A11        |             | 20      | A10      | ` 0                                                                                              |

| 21                    | A7         | 0<br>0<br>0 | 22      | A6       | 0                                                                                                |

| 23                    | A12        | 0           | 24      | A8       | 0                                                                                                |

| 25                    | A14        | 0           | 26      | A13      | 0                                                                                                |

| 27                    | A1         | 0           | 28      | AO       | 0                                                                                                |

| 29                    | A3         | 0           | 30      | A2       | U                                                                                                |

| 29<br>31              | A5         | 0           | 32      | A4       | 0                                                                                                |

| 33                    | D1         | 1/0         | 34      | DO DO    |                                                                                                  |

| 35                    | D3         | 1/0         | 36      | D2       | 1/                                                                                               |

| 37<br>39              | D5         | 1/0         | 38      | D4       | I/                                                                                               |

| 39                    | D7         | 1/0         | 40      | D6       | I/                                                                                               |

| 41                    | GND        | -           | 42      | CLOCK    | 0                                                                                                |

| 43                    | GND        | -           | 44      | SW1      | -                                                                                                |

| 45                    | +5 V       | -           | 46      | SW2      | -                                                                                                |

| 47                    | +5 V       | -           | 48      | +12V     | -                                                                                                |

| 49                    | SOUNDIN    | I           | 50      | -12V ·   | 1 -                                                                                              |

The direction of Input/Output is based on basic unit side. Reserved pins must not be used. OPEN COLLECTOR output

# o SIGNAL PIN ILLUSTRATION (Under lined signals are negative logic)

| PIN NO.                                                                                                                                                      | NAME                                                                                                                                                                 | DESCRIPTION and assessed but said                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17~32<br>33~40<br>41<br>42<br>43, 46<br>45, 47<br>48<br>49<br>50 | CST 4 CS2 4 CST2 4 CST2 4 SLTSL KESERVED RFSH WAIT INT MI BUSDIR  IORQ MERQ WK RD RESET RESERVED A0~A15 D0~D7 GND CLOCK GND CLOCK GND SW1, SW2 +5V +12V SUUNDIN -12V | RCM 4000~7FFF selected signal ROM 8000~FFFF selected signal RUM 4000~BFFF selected signal RUM 4000~BFFF selected signal For future use only. Do not use this pin. Refresh signal wait signal to CPU Interrupt request signal Fetch cycle signal of CPU This signal controls the direction of external data bus buffer when the cartriage is selected. It is low level when data is sent by the cartriage. I/U request signal Memory request signal Write signal Read signal System reset signal For future use only. Do not use this pin. Acaress bus Data bus Ground CPU clock 3.579 MHz Ground Insert/remove detection for protection +5V power supply +12V power supply Sound input (-5dbm) -12V power supply |

### NOTE

${\sf CS}$  signals imply memory request and read signal. Therefore they cannot be used chip select for writable devices such as  ${\sf RAMs.}$

#### CARTRIDGE

### 3.3 CONDITION OF CARTRIDGE CONNECTION

o Fan-in, Fan-out, (LS-TTL load)

Data and Address bus

Basic unit side

----> cartridge side

below 2

above 5

(fan-in)

<---- (fan-out)

(fan-out)

above 1/slot

below 1 ----> (fan-in)

Control Signals

(fan-out)

below 2 (fan-in)

o Voltage level

TTL level

#### CARTRIDGE

### 3.4 POWER CAPACITY

+5V

300mA/slot

+12V

50mA

-12V

50mA

MESS design uses the largest available continuous RAM area that installed from FFFF to 8000 for its system working RAM area. Units be placed in any slots including expandation slots.

Slot select register, which is port A of 8255; maps inempsical mem space to the logical CD memory space in low come unital proges). A seasele, the Inlient of value in the slot select register a slote of pages 0 and iron slot U, page 2 from slot V.

|  | 3 5 |  |  |

|--|-----|--|--|

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

|  |     |  |  |

Physical memory is always allocated to the same momory made in the advances assets in it has not possible to a locate be colffered made, page 5 or alocate to the memory apares.

o Minimum system must have two slots, one for system, the other

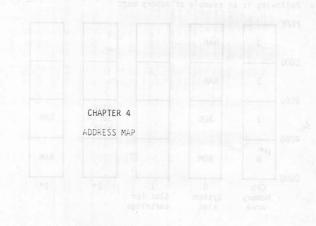

### ADDRESS MAP

#### 4.1 MEMORY MAP

o Following is an example of memory map.

- o MSX BASIC uses the largest available contiguous RAM area that is installed from FFFF to 8000 for its system working RAM area. This can be placed in any slots including expandsion slots.

- o Slot select register, which is port A of 8255, maps tnephysical memory space to the logical CPU memory space in 16K byte units (pages). For example, the following value in the slot select register allocates pages 0 and 1 from slot 0, page 2 from slot 2 and page 3 from slot 0.

Physical memory is always allocated to the same memory page in the CPU accress space. It is not possible to allocate to a different page, like page 3 of slot 3, to page 0 of CPU memory space.

o Minimum system must have two slots, one for system, the other for cartridge.

### NOTE

The word "slot" does not imply that it must have a connector for cartridges, however, a slot for cartridges must have a connector, of course. Refer to APPENDIX  $\hat{c}$ .

o MSX-DOS requires 64K RAM

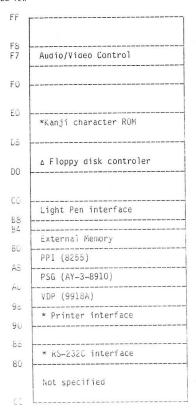

### 4.2 I/O ADDRESS MAP

#### 4.3 I/O DEVICE DESCRIPTION

#### 4.3.1 RS-232C

4.3.1.1 LSI Components = i-e251 Communication interface crip i-e253 Programmable interval timer chip

4.3.1.2 Port Address 80H R/W 8251 data port

81H R/W 5251 command/status port

82H R Baud rate setting switches

83H R Configuration setting switches

83H W Interrupt mask register

84H R/W 8253 counter 0

85H R/W 8253 counter 1

86H R/W 8253 counter 1

86H R/W 8253 counter 2

87H W 8253 mode register

4.3.1.3 The Usage of Switch Port at Address 82H And 83H -

82h read - Baud rate select

bit 0-3: baud rate for receiver bit 4-7: baud rate for transmitter

| value                 | baud rate |

|-----------------------|-----------|

| 0                     | 50        |

| 1                     | 75        |

| 2                     | 110       |

| 2 3                   | 150       |

| 4                     | 300       |

| 4<br>5<br>6<br>7<br>8 | 600       |

| 6                     | 1200      |

| 7                     | 2400      |

| 8                     | 4800      |

| 9                     | 9600      |

| Α                     | 19200     |

| В                     | N.A.      |

| C                     | N.A       |

| D                     | N.A.      |

| E                     | N.A.      |

| F                     | disable*  |

\*When value F is set as a baud rate, that function is disabled by software.

83H read - Set various functions

bit 0 - CD (carrier detect)\*

1 - auto line feed on receive\*\*

2 - Full/Half duplex

3 - XON/OFF control

4 - Word length

5 - Parity Even/Odd

6 - Parity enable

7 - Stop bit length

1 - auto line feed

1 - Full duplex

1 - Enable control

1 - 8bits, 0 - 7 bits

1 - Even

1 - Enable

1 - 2 bits, 0 - 1 bit

\* CD is a signal directly connected to carrier detect (pin 8) on the DB-25 connector.

\*\* And line feed on receiving carriage return.

#### NOTE

Bit 0 of the switch pulls up the CTS line of the 8251 (or [actually] it pulls down since CTS on 8251 is negative logic) to make it possible to send data even when CTS is not supplied from outside.

83H write - Set interrupt mask for receive

- 4.3.1.4 Usage of 8253 Timer-counter To Generate Baud Rate clock for 8251

- o Frequency of crystal

The frequency of the crystal:

1.2288 MHz

- O Usage of counter channel

CHO - Rx baud rate clock

CH1 - Tx baud rate clock

CH2 - General interrupt timer .. connect to IRO

### 4.3.2 PRINTER PORT

4.3.2.1 Port Address -

90H R Busy status : bit 1

90H W Strobe output : bit 0

91H W Print data

### ADDRESS MAP

# 4.3.3 VDP PORT

The only exception is access to the VIA. Local only but a HRP system ROM contain road and write addresses that may port. 99н К/м Сстипало and status register

# 4.3.4 PSG PORT

Actress laten beasto ad bloods and benefab for applyed Oli A1H Data write A2H Data read

ABH K/W Port A A9H R/W Port B AAH R/W Port C ABH R/W Mode registerr

# 4.3.6 External Memory (Sony)

BOH through B3H

# 4.3.7 Light Pen (Sanyo)

B8H through BBH

# 4.3.8 Audio/Visual Control

F7H BIT4 - AV CONTROL L - TV BIT5 - Ym CONTROL I - TV BIT6 - Ys CONTROL L - Super BIT7 - Video select

# 4.4 NOTES ON I/O ADDRESS ASSIGNMENT

o I/O address 80~FF are assigned for system usage. The empty areas are reserved for system use.

Although these addresses are defined here, software should not access those devices directly through the addresses listed above. Every access to the I/O must be done through the BIOS calls. This is to keep software independent from hardware differences. Manufacturers may change some hardware from the standard MSX system and is still able to maintain software compatibility

supporting the hardware differences within the BIOS, so that the difference can be transparent to software.

The only exception is access to the VDP. Locations 6 and 7 of the MSX system ROM contain read and write addresses of VDP register. The software needing to access VDP very quickly may access VDP directly through those addresses stored in ROM.

- 0 00~7F are free addresses, however when different devices use the same address, they may not be accessed at the same time. Basically, special 1/0 devices not defined here should be placed in the memory space as memory mapped 1/0. Refer to Appendix B.3.

- Δ FDC may be placed in I/O space, but it must have a mechanism to disable it and only at the moment when the system accesses the FDC, is it erabled. This makes it possible to have more than one FDC interface in the system to handle different kinds of media.

| PORT   | ыт                                                  | 1/0          | SIGN-L<br>NAME           | DESCRIPTION                          |

|--------|-----------------------------------------------------|--------------|--------------------------|--------------------------------------|

| h      | LAJAS L<br>LAJAS L<br>LAJAS L<br>LAJAS L<br>LAJAS L | 0            | CSC-                     | 000C~3FFF address slot select signal |

|        | 3                                                   | U            | CS1L<br>CS1H             | 4000~7FFF address slot select signal |

| no rei | 14.6T<br>38997<br>795 849                           | P<br>8 9 6 U | CS2L<br>CS2H             | 8000-aFFF address slot select signal |

|        | 731 "H"<br>737 "H"                                  | T            | CS3L<br>CS3H             | COOC-FFFF address slot select signal |

| В      | tnru<br>7                                           | INPUT        | ξ.<br>                   | Keyboard return signal               |

| ec no  | 1 2 3                                               | 0            | KBC<br>KB1<br>KB2<br>KB3 | Keyboard scan signal                 |

|        | 4.4                                                 | U            | CASUN                    | Cassette control signal (L-ON)       |

|        | 5                                                   | P            | CASh                     | Cassette write signal                |

|        | 6                                                   | T            | CAPS                     | CAPS lamp signal ( "L"> ON )         |

|        | 7                                                   |              | SOUND                    | Sound input by software              |

# 4.6 PSG BIT ASSIGNMENT

| PORT | BIT         | 1/0    | CONNECTOR PIN NO.                               | NOTE                                |

|------|-------------|--------|-------------------------------------------------|-------------------------------------|

| А    | 0           | I      | J3-PIN 1 1<br>J4-PIN 1 * 2                      | FWD1<br>FWD2                        |

| lane | 1           | N      | J3-PIN 2 1<br>J4-PIN 2 * 2                      | BACK1<br>BACK2                      |

|      | 2           | Р      | J3-PIN 3 1<br>J4-PIN 3 * 2                      | LEFT1<br>LEFT2                      |

|      |             | U      | J3-PIN 4 1<br>J4-PIN 4 * 2                      | RIGHT1<br>RIGHT2                    |

|      | 4           | Т      | J3-PIN 6 1<br>J4-PIN 6 * 2                      | TRGA1<br>TRGA2                      |

|      | 5           |        | J3-PIN 7 1<br>J4-PIN 7 * 2                      | TRGB1<br>TRGB2                      |

|      | 6<br>7      |        | KEY LAYOUT Select 4<br>CSAR (CASSETE TAPE READ) | Japanese version only               |

| В    | 0           | 300    | J3-PIN 6 3<br>J3-PIN 7 * 3<br>J4-PIN 6 3        | "H" LEVEL<br>"H" LEVEL              |

|      | 2           | 0<br>U | J3-PIN / * 3<br>J4-PIN 6 3                      | "H" LEVEL                           |

|      | 2<br>3<br>4 | T      | J4-PIN 7 * 3                                    | "H" LEVEL                           |

|      | 4           | Р      | J3-PIN 8                                        | Turnet unns                         |

|      | 5           | U      | J4-PIN 8 *                                      |                                     |

|      | 6           | T      | PORT A INPUT SELECT<br>KLAMP (KANA LAMP L- ON)  | Selects J3/J4 Japanese version only |

1 Available when bit 6 of port B is low used by JOYSTICK1

2 Available when bit 6 of port B is high used by JOYSTICK2 3 Turn to "H" level when use those pins as an input port.

Tied an open collector buffer to the output. (Refer to Appendix C-1) 4 JIS layout - "H" level, syllable layout - "L" level

PIN5 +5V <Remark> PIN9 GND

o On the minimum system, there is no J4 connector.

# APPENDIX A

# LIST OF CONNECTORS

| PIN NAME                         | SPECIFICATION                                   |  |

|----------------------------------|-------------------------------------------------|--|

| Video output and composite video | DIN 5 PIN CONNECTOR 4 or<br>RCA 2 PIN CONNECTOR |  |

| 2. RF modulated signal           | RCA 2 PIN CONNECTOR                             |  |

| CASSETTE                         | DIN 8 PIN CONNECTOR (DIN-45326)                 |  |

| I/O PORT                         | AMP 9 PIN CONNECTOR                             |  |

| PRINTER -                        | AMPHENOL 14 PIN CONNECTOR                       |  |

| CARTRIDGE BUS                    | 0.10 INCH (2.54mm) SPACE, 50 PIN CONNECTOR      |  |

| AUDIO                            | RCA 2 PIN CONNECTOR                             |  |

# Δ DIN 5 PIN CONNECTOR SIGNAL PIN ASSIGNMENT

| IN NO. | NAME     | PIN CONNECTION         |

|--------|----------|------------------------|

| 1      | +5 V     |                        |

| 2      | GND      | <b>② ⑤</b>             |

| 3      | AUDIO    | ©                      |

| 4      |          | 9 8 MEQ 000 2. QEVO 00 |

| 5      | RF VIDEO |                        |

### APPINDIA E

# NOTES ON SYSTEM EXPANSION

### **B.1 RAM EXPANSION**

- The MSX BASIC needs contiguous RAM space starting from FFFF down to 6000. Therefore, additional RAM should be added to existing RAM to form contiguous RAM space.

- o If the basic model has only 8K bytes of RAP, it is not possible to add RAM in the slot other than the original 8K in place, because the slot select logic treats memory space in 16K byte units. So an expansion cartridge that has 16K bytes adds only 8K bytes when it is placed at location C000 to FFFF. It is not possible to expand the RAM area by placing it at location 8000 to BFFF because there would be no RAM from C000 to DFFF. So cartridges for 16 KB basic systems, off the shelf, cannot be used on this 8 KB RAM system. Therefore it is important to make this point clear to the user. We don't recommend building a system which has only 8K bytes.

- o The BASIC MSX software only uses RAM from 8000 to FFFF, so the RAM installed from 0 to 7FFF cannot be used by it.

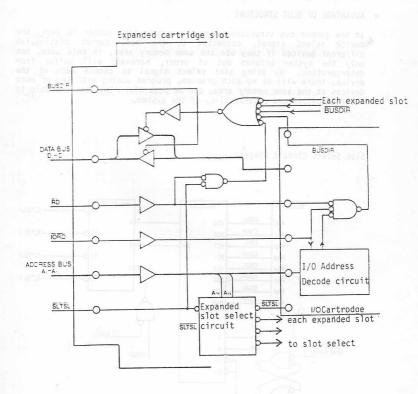

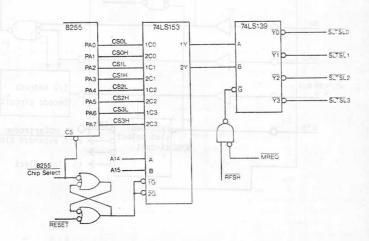

# **B.2 SLCT EXPANSION**

- o To expand slots, the additional slots are expanded from a primary slot. Primary slots are those slots which are managed by the basic slot select register placed in port A of 5255. Increfore, to select the expanded slot, first select the primary slot to which the expanded slot is connected, and select the desired expansion slot.

- o The location of the slot select register for the expanded slots is at memory address FFFF of the primary slot. To make it possible to differentiate this register from ordinary RAM, complement the output of the register. That is, when reading the register, the read data is the complement of the actual value of the register.

- o The maximum number of cartridges that can be connected to the cartridge

bus is four. Therefore, buffers are necessary to put more than five slots to the system. The control signal that controls the direction of those buffers is BUSDIR. Those devices which send signals to the CPU and are placed in an expanded slot have to send BUSDIR signal as well the change the direction of the buffer from expanded slots to CPU. However, for the accesses to memory, it is possible to know the direction of the bus using the slot select signal to the primary slot, memory request signal and read/write signal. So the direction of the buffer should be controlled around the buffer circuitry. So, those cartridges which contain only ROM/RAM do not have to manage BUSDIR signal, so that make the cost of them cheap. But those cartridges that contain some devices which send signals to the CPU, that is, those devices that respond to INP instruction or those devices that is responsible to supply the address in response to the mode 2 of interrupt must force BUSDIk at 'L' level when they send data to CPU.

# B.3 I/O EXPANSION

o In Z-80 based system, it is common to place I/O devices in I/O address space. But the MSX system design is so flexible and expandable, it is possible to agg some I/O devices with cartridge that share same address space. If this is the case, none of those devices can be accessed

properly.

To avoid this situation, it is preferred to place I/O devices in the memory spaces because they are managed by slot select logic and no memory can be accessed simultaneously when they are placed in different slots. But the devices that placed in memory space cannot be accessed by the softwares that run in different slots. So those devices that are general to any software such as VDP have to be placed in 1/0 address space. Also in some case, it is cheaper to use 1/0 address space because only 8 bits address information should be decoded. We defined 1/0 address space from 80 to FF for those system devices. But the addresses below 7F are left free. Anybody may use this address space, but nobody can tell you that somebody uses same address that you are using. So we recommend to use memory address spaces rather than I/O address space. We will assign the reserved address to those devices that is thought as MSX standard device.

# B.5 SLOT

### o CONCEPT OF SLOT

For a structure of 64 KB memory space, the concept of slot and memory bank is nearly the same. But CPU can choose the cartridge by the slot number in which it is inserted.

The slot concept is originated from the standpoint of the software, and so, the software is independent to the number of slot that has actual slot opening.

# o ADVANTAGE OF SLOT STRUCTURE

In the common bus structure, when the memory bank number is even, the device select signal, connected to the bus, cannot distinguish different devices if they use the same memory area, in this case, not only the system becomes out of order, hardware will suffer from deterioration. By using slot select signal to choose each of the device, there will be no such problem, program dueing with two or more devices at the same memory area, can be possible. This is favorable to the flexibility and expandability of the system.

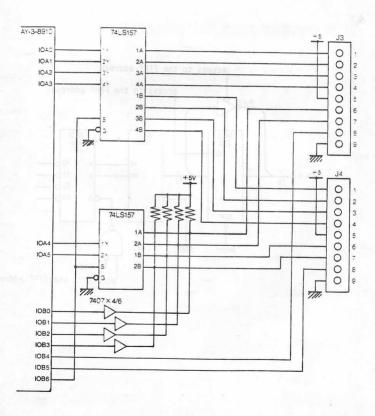

Slot Select Circuit Diagram

SAMPLE CIRCUIT DIAGRAM OF GENERAL I/O PORT

APPENDIX D

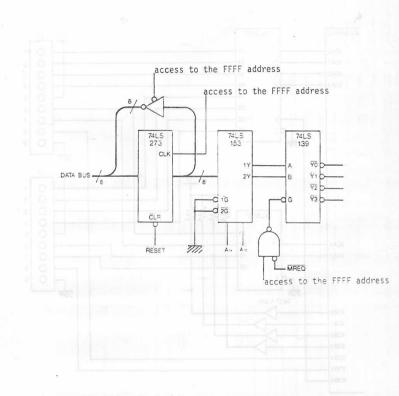

# SAMPLE CIRCUIT DIAGRAM OF EXPANDED SLOT SELECT SIGNAL GENERATE LOGIC

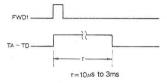

# APPENDIX E GAME PADDLE TIMING DIAGRAM